At the Supercomputing 2021 (SC21) event, Intel has disclosed further important details about Sapphire Rapids and Ponte Vecchio processors. Fittingly for the event, these processors are aimed at accelerating datacentres and supercomputers, but are still of some interest to PC enthusiasts due to the inevitable trickle down of the technologies involved.

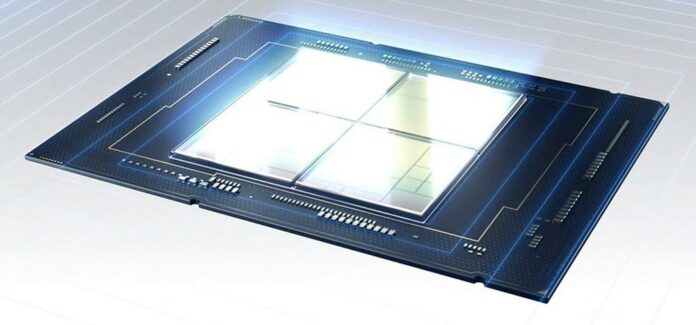

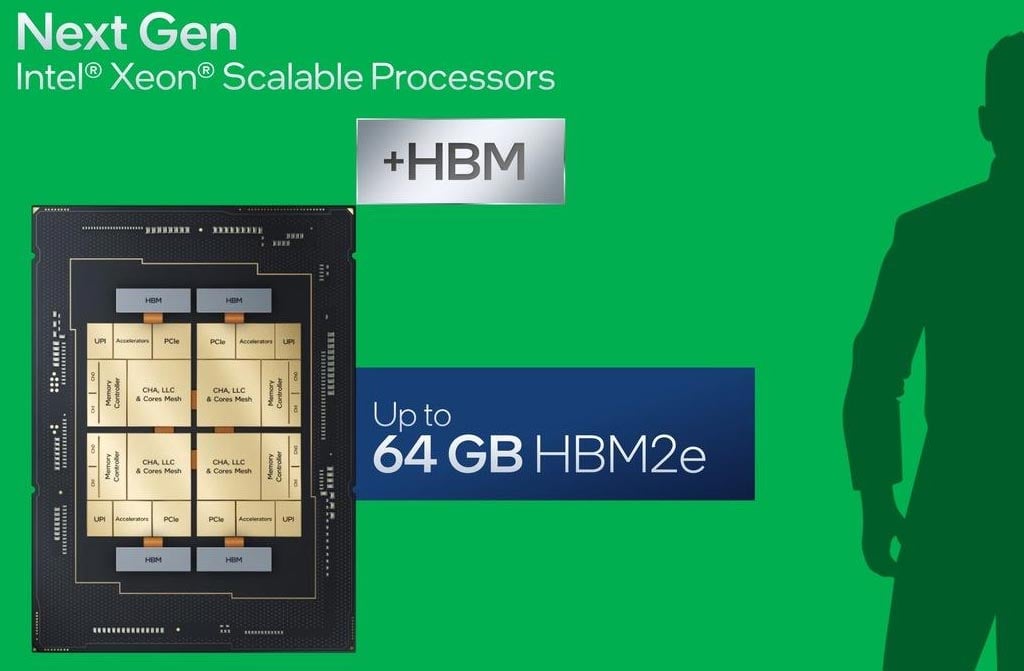

Intel previously revealed some details about Sapphire Rapids, but raised some eyebrows at SC21 with the revelations these HPC processors will come with up to 64GB HBM2e on the package (four chips), next to the four compute tiles, all connected via EMIB. HBM2e offer bandwidth of up to 460GB/s per stack, with four packages theoretically offering up to 1.84TB/s throughput. With Intel saying “up to” 64GB HBM2e, one might expect lower-rung members of the Sapphire Rapids family of Xeons to come with less on-die memory, say 32GB, 16GB, or even none – thus supporting DDR5 only. Intel didn’t talk of any specific next-gen Xeon SKUs at SC21 though.

Users will be able to run Sapphire Rapids Xeon CPUs with HBM2e in three modes; HBM-only mode when a calculation can fit into the onboard HBM2e memory, Flat mode when the HBM and DDR5 are used in a continuous addressable space, or Cache mode where the on-chip HBM is used as a cache for the DDR5.

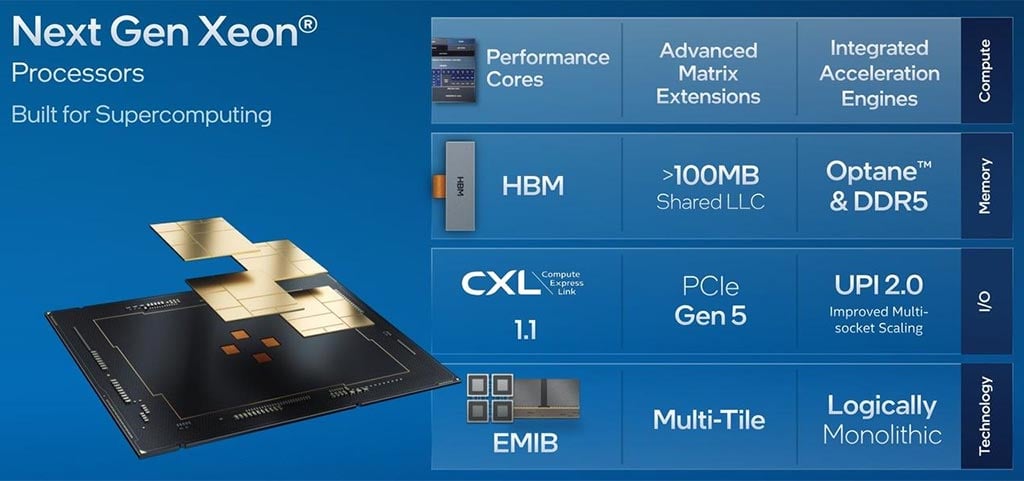

Recapping the other Sapphire Rapids Xeon specs, the quad clusters will come packing Golden Cove P-cores, have up to 100MB or more of L3 cache, support eight channels of DDR5, PCIe 5.0, Optane memory, and CXL 1.1 – all in a logically monolithic package.

Ponte Vecchio

Intel Ponte Vecchio is outlined in more detail than ever in the slide above, broken down into compute, memory, I/O, and underlying tech categories. Highlights are this GPU accelerator’s 128 RT units and 128 Xe cores, up to 64MB L1 cache, up to 408MB L2 cache and support for HBM2e memory. This EMIB/Foveros tech product will be fabricated from a mix of Intel 7 and TSMC N5/N7 silicon.

The upcoming DoE Aurora Supercomputer, designed by Intel and Cray, will feature >54,000 Ponte Vecchio GPUs and >18,000 Sapphire Rapids processors. Aurora will be able to wield up to 2 ExaFLOPs of computing power.

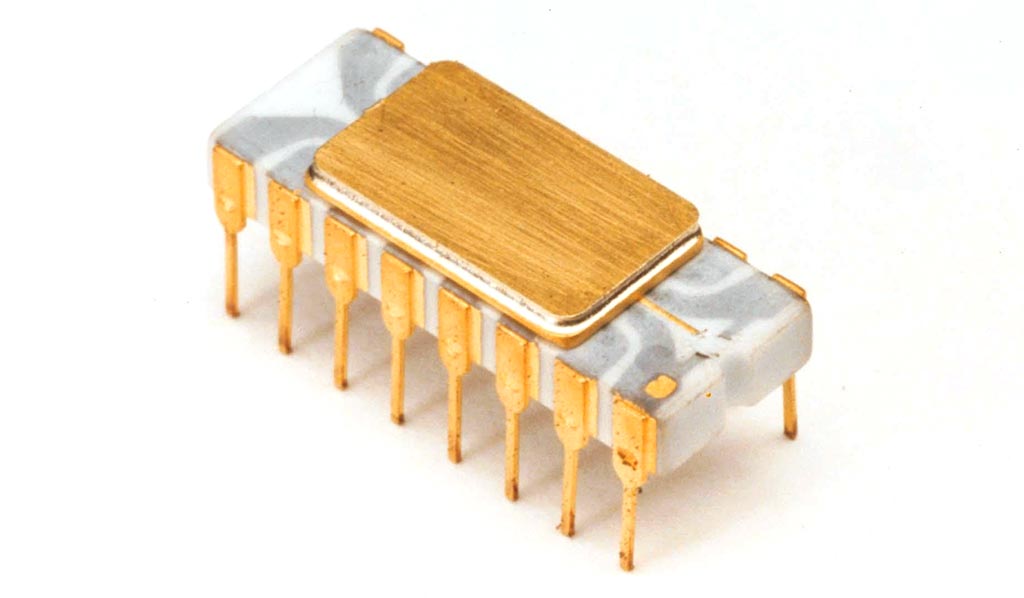

Intel 4004 microprocessor hits 50

Intel’s first commercially available microprocessor, the Intel 4004, is 50 years old. The Intel 4004 was originally designed for the Nippon Calculating Machine Corp, to power a calculator, and was priced at US$60.

Intel’s fingernail-sized 16-pin single-core 4-bit chip was made using 10μm fabrication technology, used 2in P-channel silicon-gate MOS technology, featured 2,250 transistors, and ran at 750kHz.

In addition to the Intel blog about the 50th birthday of the 4004 microprocessor, YouTuber der8auer has some interesting content – where he “delids” one of these ancient artefacts. Check out der8auer’s video above.

On Twitter, HardwareLuxx Editor Andreas Schilling put forward an interesting idea for Intel, that isn’t without precedent. Schilling suggested Intel releases an anniversary edition of an Alder Lake CPU. His dreams didn’t end with the idea of the name – the Intel Core i9-124004, Schilling proposed the following core configuration; 40 E-cores, and 04 P-cores…