A recent Linux compiler for Intel’s upcoming Nova Lake has attracted attention due to its lack of flags regarding the AVX10, APX, and AMX instructions, suggesting that they may be absent from these chips. While this wouldn’t be surprising considering the company’s past behaviour – disabling AVX-512 on consumer parts to give server CPUs an advantage, for example – it was believed that future Intel hardware would support AVX10 along with 512-bit AVX-512.

According to this early enablement patch, the Nova Lake architecture will only support the following extensions:

“MOVBE, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, POPCNT, AES, PREFETCHW, PCLMUL, RDRND, XSAVE, XSAVEC, XSAVES, XSAVEOPT, FSGSBASE, PTWRITE, RDPID, SGX, GFNI-SSE, CLWB, MOVDIRI, MOVDIR64B, WAITPKG, ADCX, AVX, AVX2, BMI, BMI2, F16C, FMA, LZCNT, PCONFIG, PKU, VAES, VPCLMULQDQ, SERIALIZE, HRESET, AVX-VNNI, UINTR, AVXIFMA, AVXVNNIINT8, AVXNECONVERT, CMPCCXADD, AVXVNNIINT16, SHA512, SM3, SM4 and PREFETCHI.”

AVX10 (Advanced Vector Extensions) is Intel’s next-gen vector/SIMD extension intended to offer wider, more consistent vector capabilities across hybrid cores. It addresses several issues of AVX-512 while delivering higher performance in compute tasks, content creation, and even some game engines.

APX (Advanced Performance Extensions) expands the entire x86 instruction set with access to more general-purpose registers, adding new features that improve general-purpose performance. It does so by doubling the number of registers (GPRs) from 16 to 32, allowing the compiler to keep more values in them. As a result, code compiled with APX contains 10% fewer loads and 20% fewer stores compared to code compiled for an Intel 64 baseline. This makes it valuable for real-time or latency-sensitive applications, games, and databases.

AMX (Advanced Matrix Extensions) is a matrix-acceleration ISA aimed at large matrix multiplies, important for ML workloads. It can speed up machine-learning frameworks, such as AI inference.

Now, while Intel is still finalising its next-gen Nova Lake specifications, the chips’ microarchitecture is already fixed, meaning that they won’t magically add these instructions later. That said, previous documents have indicated Intel will introduce AVX10.2 support in future Intel Core processors, so who is right? What is sure is that Nova Lake would benefit from AVX10, APX, and AMX support, if not today, then later.

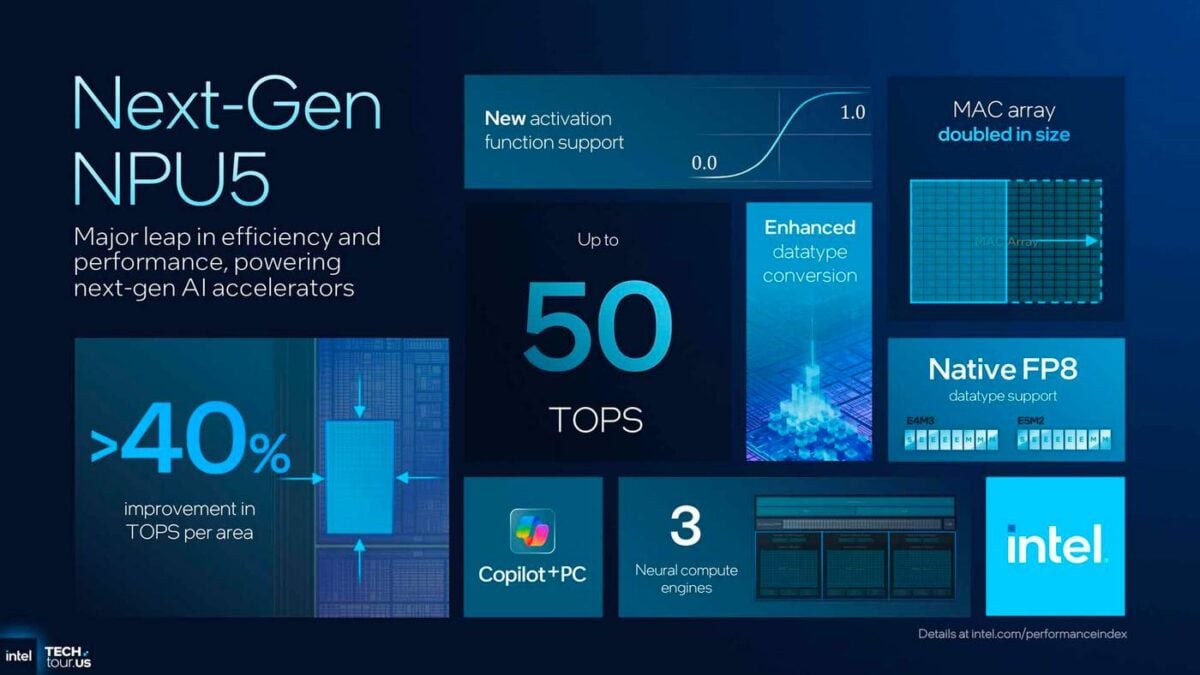

With up to 52 cores under the hood and the latest instruction support, the ‘Cora Ultra 400’ Nova Lake CPUs could be a worthy contender to AMD’s Zen 6 and Zen 7, which should support at least AVX512 like their predecessors. Nova Lake is also expected to feature a sixth-gen NPU (Neural Processing Unit) design, which should allow more local AI capabilities, likely offering above the 50 TOPS of fifth-gen NPUs.

Nova Lake chips are expected to launch in late 2026 or early 2027, continuing Intel’s hybrid core design, manufactured using a mix of Intel’s 18A and TSMC N2 nodes. Even if they end up lacking these instructions, they should still fly through typical consumer tasks thanks to their raw power. We can’t wait to see them in action.